Data Flow Modelling in Verilog

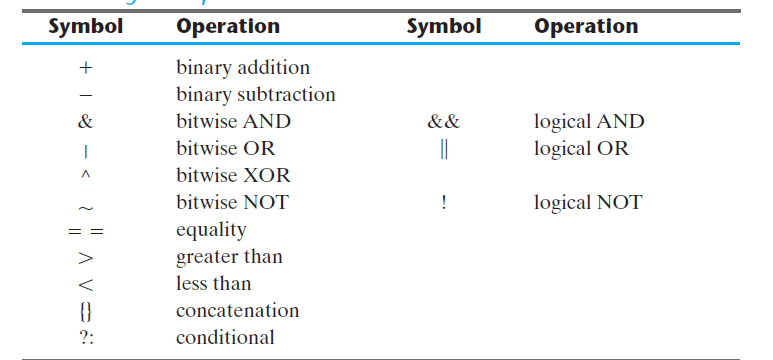

Verilog provides 30 different types of Operators. Learn to design Combinational circuits using data Flow modelling.

What Is The Difference Between Data Flow And Behavioral Modelling In Verilog Hdl Ee Vibes

Just like an AND gate an OR gate can have any number of input probes but only one output probe.

. It is a setup to test our Verilog code. A logical OR operation has a high 1 output when one or both of the gates inputs are high 1. Module fulladder input a input b input cin output s output cout.

It is used to describe combinational circuits. Instead of using directly in data flow we use operations such as Bit-Wise AND Multiply Modulus Plus - Minus Logical AND etc in Data Flow modelling. Theres no need for data-.

Module AND_2_data_flow output Y input A B. This approach allows the designer to focus on optimizing the circuit in terms of the flow of data. Gate level modelling is compared with Data flow modelling with the help of few exampleslin.

Data flow modeling. In this video 4-bit Adder has been designed and simulated using Data Flow Modelling. Verilog Code for Full Subtractor using Dataflow Modeling.

But before starting to code we need proper knowledge of basic logic gates in Verilog. They are Dataflow Gate-level modeling and behavioral modeling. The design is compared with hierarchical design.

Verilog full adder in dataflow gate level modelling style. Dataflow modeling has become a popular design approach as logic synthesis tools became sophisticated. It includes the Verilog file for the design.

Remember that a module is a basic building block in Verilog. We would again start by declaring the module. An OR gate is a logic gate that performs a logical OR operation.

Testbench in Verilog of a half-subtractor. Dataflow modeling uses a number of operators that act on operands to produce the desired. The dataflow level shows the nature of the flow of data in continuous assignment statements.

However in complex design designing in gate-level modeling is a challenging and highly complex task and thats where data-flow modeling provides a powerful way to implement a design. Dataflow modeling uses expressions instead of gates. Half adder is a combinational arithmetic circuit that adds two numbers and produces a sum bit S and carry bit C as the output.

Full Adder in Dataflow model. The test bench is the file through which we give inputs and observe the outputs. Verilog Language is a very famous and widely used programming language to design digital IC In this verilog tutorial level of abstraction has been covered.

While the gate-level and dataflow modeling are used for combinatorial circuits behavioral modeling is used for both sequential and combinatorial circuits. First of all we declare the module. Assign couta.

We start by writing include which is a keyword to include a file. Endmodule Just like the and operation the logical operator performs a binary multiplication of the inputs we write. To start with this first you need to declare the module.

To declare the module we have a keyword module then we write the identifier or the name of the module in this way. Verilog allows a circuit to be designed in terms of the data flow between registers and how a design processes data rather than the instantiation of individual. Verilog code for 21 MUX using data flow modeling.

The two basic logic gates are AND and OR gates in which the name suggested. The following figure shows a basic NAND gate Gate Level Modeling Data Flow Modeling Behavioural Modeling RTL Simulation and Truth Table of NAND. Then we use assignment statements in data flow modeling.

Verilog code for AND gate using data-flow modeling. To get familiar with the dataflow and behavioral modeling of combinational circuits in Verilog HDL Background Dataflow Modeling Dataflow modeling provides the means of describing combinational circuits by their function rather than by their gate structure. So if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this.

The first line is. Data flow modelling in Verilog and Implementation of BCD Adder in Xilinx ISE. There are three types of modeling for Verilog.

Handling multi-bit data Concatenation to group data. Dataflow modeling in Verilog allows a digital system to be designed in terms of its function. Dataflow modeling makes use of the functions that define the working of the circuit instead of its gate structure.

Assign Y A. Dataflow modeling utilizes Boolean equations and uses a number of operators that can acton inputs to produce outputs operators like -. If neither input is high the output is low 0.

Lecture 4 Dataflow And Behavioral Modeling I Youtube

Veriloghdl Basic Data Flow Modelling Youtube

Verilog Part 1 Example Dataflow And Structural Description Youtube

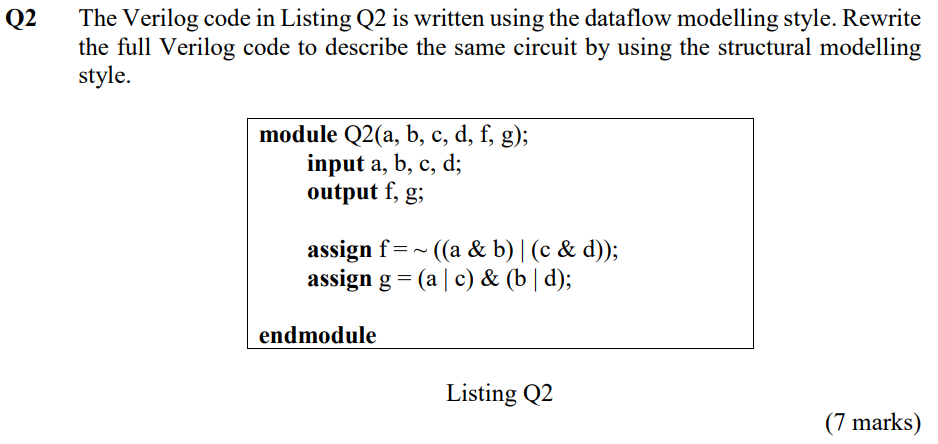

Solved The Verilog Code In Listing Q2 Is Written Using The Chegg Com

0 Response to "Data Flow Modelling in Verilog"

Post a Comment